Journal of Electrical and Computer Engineering Innovations (JECEI) Journal homepage: http://www.jecei.sru.ac.ir

**Research paper**

# Modified Topologies for Single Source Switched-Capacitor Multilevel Inverters

# F. Sedaghati<sup>1,\*</sup>, S. Ebrahimzadeh<sup>1</sup>, H. Dolati<sup>2</sup>

<sup>1</sup>Department of Electrical Engineering, Faculty of Engineering, University of Mohaghegh Ardabili, Ardabil, Iran. <sup>3</sup>Faculty of Electrical and Computer Engineering, University of Tabriz, Tabriz, Iran.

| Article Info                                                                                                                        | Abstract                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|-------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Article History:<br>Received 01 September 2024<br>Reviewed 03 October 2024<br>Revised 15 November 2024<br>Accepted 17 November 2024 | <b>Background and Objectives:</b> Increasing environmental problems and challenges<br>have led to increased use of renewable energy sources such as photovoltaic or PV<br>system. One of the attractive research fields is power electronic converters as<br>interfaces for renewable energy sources. Multilevel inverters can operate as such<br>interfaces. This paper introduces modified topologies of switched-capacitor<br>multilevel inverters, designed to overcome constraints of low voltage renewable<br>energy sources such as PV.                                                                                                                   |

| <b>Keywords:</b><br>Multilevel inverter<br>Switched-capacitor<br>Capacitor charging<br>Longest discharge period                     | Methods: Configuration of topologies utilize a single DC source with series or parallel connection of capacitors to produce 7-level, 9-level, and 11-level voltage in the converter load side. The paper presents the converter operation principle, elements voltage stress analysis, and capacitor sizing calculations. Also, operation analysis of suggested inverter topologies is validated using implemented set up. <b>Results:</b> Comprehensive comparative analysis reveals that the proposed topologies have merits and superior performance compared to existing solutions regarding component number, voltage boost factor, and voltage stress. The |

| *Corresponding Author's Email<br>Address:<br>farzad.sedaghati@uma.ac.ir                                                             | <ul> <li>experimental measurement results confirm the accuracy of multilevel output voltage waveforms and the self-balancing of capacitor voltages, as predicted by theoretical analysis.</li> <li>Conclusion: The suggested switched-capacitor multilevel inverters, moreover the superiority over previously presented topologies, show great potential for application in photovoltaic systems and electric vehicle battery banks.</li> </ul>                                                                                                                                                                                                                 |

This work is distributed under the CC BY license (http://creativecommons.org/licenses/by/4.0/)

# Introduction

In order to achieve zero carbon emissions, renewable energy sources have gained noteworthy regard due to their dependable performance, minimal ecological footprint, cost efficiency, and adaptability within systems. Increasing adoption of renewable energy sources and electric vehicles has led to a growing need for enhanced voltage boost capability. Nevertheless, most of DC sources such as solar cells and EV batteries have a restricted capacity for boosting power, indicating the need for immediate improvements in this field [1]-[3]. Commercial solutions in this field typically use twostage power conversion, utilizing a step-up converter. In order to get the highest possible output voltage, the components utilized in these converters operate at high switching frequencies, which increase power losses and prices [4]. The impedance source inverter, which employs LC units, incurs additional system volume and expense. In addition, the converters' two-level setup results in high total harmonic distortion (THD) and power losses. The high rate of voltage variation (dv/dt) in switches increases power losses during switching, and also, increases voltage stress and electromagnetic interference (EMI), and impaired reliability. Ultimately, this can lead to reduction in lifespan of electric vehicles or motors [5]-[8].

Industry commonly utilizes multilevel inverters, including traditional diode-clamp, flying-capacitor, and cascade H-bridge topologies. These inverters offer several benefits, such as low output voltage THD, less switching stress, and lower operating frequency. Traditional configurations of multilevel inverters cannot enhance the input voltage [5]-[8].

An innovative multilevel inverter utilizing switched capacitor (SC) approach was provided as a solution to address the abovementioned limitations [9]-[11]. SC multilevel inverters offer the following benefits:

- Capacitor voltage self-balance: This feature guarantees that the voltage across every capacitor in the inverter is similar, hence preserving the stability of the inverter [12], [13].

- The inverter does not utilize significant magnetic components and transformers, resulting in lighter and smaller sizes, enhancing its portability and compactness [12], [14], [15].

- Offer a high degree of flexibility as they can be quickly adjusted to match the individual needs of various applications [16], [17].

- SC multilevel inverters provide the ability to boost the input voltage, which distinguishes them from traditional multilevel inverters [12], [18], [19].

SC multilevel inverters have some demerits, such as employing high count of active and passive elements, and capacitor voltage balancing concerns [20]. However, they are still highly regarded for their merits and have been proposed for use in high-power photovoltaic systems [21].

A multilevel inverter including SC cells was introduced in [22]. This inverter can be constructed in symmetric or asymmetric configurations and possesses the capability to expand up to greater levels. Its main advantage is low voltage stress on its switches. Nevertheless, the primary disadvantages of this system consist in its extensive utilization of numerous switches and the inclusion of unidirectional switches. A topology capable of producing a voltage with seven distinct levels and a voltage boost factor of 3 has been suggested in [23]. This is accomplished by utilizing only four high-frequency switches, which are secured by low-voltage capacitors. Nevertheless, this configuration experience significant voltage stress on the switches and also, necessitate additional passive components. Consequently, size and weight of the converter are increased. A seven-level inverter design was suggested in [24] for use in mediumvoltage scenarios, particularly for high-power applications. The configuration includes eight operational

switches, two internal flying-capacitor units, and two diodes. However, this topology has two primary disadvantages: the use of two unidirectional current switches and the imposition of considerable voltage stress on the switch.

In [25], a generalized boost multilevel inverter that can be utilized in applications with low-voltage input sources.

By controlling the parallel and series connection of capacitors and DC sources, this configuration can produce high voltage levels.

The important demerit of this topology is utilizing high count of passive elements, which increases the converter cost, size, and weight. The single-phase SC MLI proposed in [26] can produce a nine-level AC voltage with a voltage gain of 4 in the output. This 9-level topology is achieved by modifying the switching algorithm of the 13-level configuration introduced in [26].

However, this topology has essential downside as it requires a large number of switches, which in turn increases the need for gate drivers, and subsequently, the cost and size of the converter. A 9-level inverter was introduced in [27], which offers the significant advantage of zero current switching for charging capacitors. However, its primary drawback is utilization of high count of switches, diodes, capacitors, and switches with very high total standing voltage (TSV). According to the configuration presented in [28], 11-level switchedcapacitor multilevel inverter can produce an output voltage waveform using 14 switches, 3 capacitors, and 2 diodes. However, this topology has a major drawback of using a lot of switches and a low boost factor. A singlephase switched-capacitor based 11-level inverter topology is presented in [29].

This configuration offers increased levels, a quintuple voltage boost factor, and natural capacitors voltagebalancing as its main features. However, due to the inclusion of more passive elements and high TSV, power loss, cost, and volume are increased. The 11-level topology that uses the SC technique, described in [30], offers several benefits including capacitor voltage selfbalancing and high boost efficiency. However, because of large number of power switches and high TSV, the converter experiences high power losses that consequently reduce efficiency.

The rest of the paper is organized as follows: In section 2, proposed multilevel inverter topology and operation are described. Section 3 presents extended topology of suggested converter. Capacitor sizing calculations is given in section 4, and converter power losses are computed in section 5. Section 6 presents comprehensive comparison of the introduced converter with similar topologies. Experimental test results are illustrated in section 7, and section 8 concludes the paper.

#### **Proposed 7-Level Inverter Topology**

#### A. Circuit Description

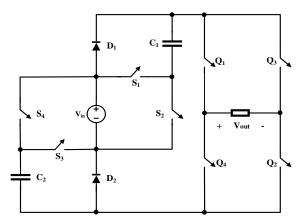

Circuit schematic of proposed boost multilevel inverter is illustrated in Fig. 1. Suggested 7-level topology contains a DC voltage source,  $V_{in}$ , two capacitors, C<sub>1</sub> and C<sub>2</sub> along with the voltage source with two power diodes, and eight power semiconductor switches to produce 7-level voltage in the output. Capacitors C<sub>1</sub> and C<sub>2</sub> have equal capacity and are charged in the same manner. Proposed MLI generates output voltage with levels of  $\pm V_{in}$ ,  $\pm 2V_{in}$ , and  $\pm 3V_{in}$  by H-bridge inverter. Different switching modes for the suggested topology to produce 7-level output voltage are shown in Table 1. All switches used in this configuration have the ability to facilitate bidirectional current so, the converter supports the inductive load with reverse current flow.

Fig. 1: Configuration of proposed 7-level switched-capacitor inverter.

| $rac{V_o}{V_{in}}$ |       | Switch and diode state |       |       |       |    |       |                       |       |       |       | Capacitor<br>state |  |  |

|---------------------|-------|------------------------|-------|-------|-------|----|-------|-----------------------|-------|-------|-------|--------------------|--|--|

| v in                | $S_1$ | $S_2$                  | $S_3$ | $S_4$ | $Q_1$ | Q2 | $Q_3$ | <b>Q</b> <sub>4</sub> | $D_1$ | $D_2$ | $C_1$ | C <sub>2</sub>     |  |  |

| +3                  | 1     | 0                      | 1     | 0     | 1     | 1  | 0     | 0                     | R     | R     | D     | D                  |  |  |

| +2                  | 1     | 0                      | 0     | 1     | 1     | 1  | 0     | 0                     | R     | F     | D     | С                  |  |  |

| +1                  | 0     | 1                      | 0     | 1     | 1     | 1  | 0     | 0                     | F     | F     | С     | С                  |  |  |

| +0                  | 0     | 1                      | 0     | 1     | 1     | 0  | 1     | 0                     | F     | F     | С     | С                  |  |  |

| -0                  | 0     | 1                      | 0     | 1     | 0     | 1  | 0     | 1                     | F     | F     | С     | С                  |  |  |

| -1                  | 0     | 1                      | 0     | 1     | 0     | 0  | 1     | 1                     | F     | F     | С     | С                  |  |  |

| -2                  | 1     | 0                      | 0     | 1     | 0     | 0  | 1     | 1                     | R     | F     | D     | С                  |  |  |

| -3                  | 1     | 0                      | 1     | 0     | 0     | 0  | 1     | 1                     | R     | R     | D     | D                  |  |  |

Table 1: Circuit elements states for 7-level topology operation.

# B. Operation Principle

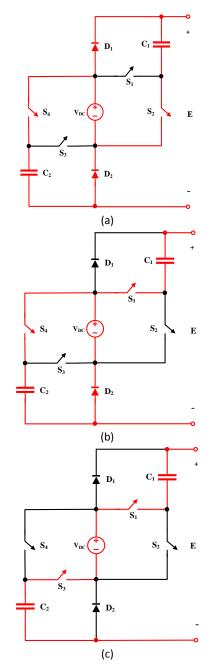

Operation of the introduced 7-level inverter with charge and discharge cycles of capacitors at each generated voltage level is given in Fig. 2. Switching operation of switches  $S_1$ ,  $S_2$ , and switches  $S_3$ ,  $S_4$  are complementary which simple control. The switches in the flow path are marked in red colour in Fig. 2.

**Mode 1:** In this mode, both switches  $S_2$  and  $S_4$  are on, causing the capacitors to be charged equally using the source as the current flows through the diodes. The output voltage at the "*E*" terminal equals the source voltage level (Fig. 2(a)).

**Mode2:** Switches  $S_1$  and  $S_4$  are on in this mode that keeps capacitor  $C_2$  charged. Due to the capacitor  $C_1$  being in series with the  $V_{in}$ , voltage level of  $2V_{in}$  is generated in terminal *E* (Fig. 2(b)).

**Mode 3:** This mode involves connecting capacitors  $C_1$  and  $C_2$  in series with  $V_{in}$  and discharging them to generate voltage level  $3V_{in}$  in terminal by turning on switches  $S_1$  and  $S_3$  (Fig. 2(c)).

Fig. 2: Equivalent circuits of proposed inverter for each output voltage level, (a) mode 1, (b) mode 2, (c) mode 3.

# C. Voltage Stress Analysis

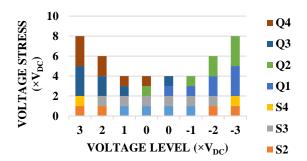

Table 2 presents voltage stress of semiconductor elements applied in the 7-level configuration. Also, Fig. 3 illustrates TSV values of the diodes and switches. It indicates that switches  $S_1$ - $S_4$  have the same voltage stress, equals to  $V_{dc}$ . On the other hand, switches  $Q_1$ - $Q_4$ , which forms the H-bridge in the output, bears varying voltage stress in each step, with the maximum voltage stress of  $3V_{dc}$ . TSV of the proposed 7-level configuration is obtained as given in the following:

$$TSV = 4 \times V_{dc} + 4 \times 3V_{dc} = 16V_{dc} \tag{1}$$

Fig. 3: Voltage stress of switches in the suggested 7-level topology.

Table 2: Circuit elements states for 9-level topology operation

| $rac{V_o}{V_{in}}$ | Switch and diode state |       |                |       |                |                |    |                |    |            | Capacitor state |       |                |    |                |                |

|---------------------|------------------------|-------|----------------|-------|----------------|----------------|----|----------------|----|------------|-----------------|-------|----------------|----|----------------|----------------|

| $V_{in}$            | $S_1$                  | $S_2$ | S <sub>3</sub> | $S_4$ | S <sub>5</sub> | S <sub>6</sub> | Q1 | Q <sub>2</sub> | Q₃ | <b>Q</b> 4 | $D_1$           | $D_2$ | D <sub>3</sub> | C1 | C <sub>2</sub> | C <sub>3</sub> |

| +4                  | 1                      | 0     | 1              | 0     | 0              | 1              | 1  | 1              | 0  | 0          | R               | R     | R              | D  | D              | D              |

| +3                  | 1                      | 0     | 0              | 1     | 1              | 0              | 1  | 1              | 0  | 0          | R               | R     | F              | D  | D              | С              |

| +2                  | 1                      | 0     | 0              | 1     | 0              | 1              | 1  | 1              | 0  | 0          | R               | F     | F              | D  | С              | С              |

| +1                  | 0                      | 1     | 0              | 1     | 0              | 1              | 1  | 1              | 0  | 0          | F               | F     | F              | С  | С              | С              |

| +0                  | 0                      | 1     | 0              | 1     | 0              | 1              | 1  | 0              | 1  | 0          | F               | F     | F              | С  | С              | С              |

| -0                  | 0                      | 1     | 0              | 1     | 0              | 1              | 0  | 1              | 0  | 1          | F               | F     | F              | С  | С              | С              |

| -1                  | 0                      | 1     | 0              | 1     | 0              | 1              | 0  | 0              | 1  | 1          | F               | F     | F              | С  | С              | С              |

| -2                  | 1                      | 0     | 0              | 1     | 0              | 1              | 0  | 0              | 1  | 1          | R               | F     | F              | D  | С              | С              |

| -3                  | 1                      | 0     | 0              | 1     | 1              | 0              | 0  | 0              | 1  | 1          | R               | R     | F              | D  | D              | С              |

| -4                  | 1                      | 0     | 1              | 0     | 0              | 1              | 0  | 0              | 1  | 1          | R               | R     | R              | D  | D              | D              |

# **Extended Topology**

# A. Extended 9-Level Topology

As mentioned before, using multiple DC sources to get more levels in the output voltage is one of demerits of the multilevel inverters. However, in the extended topology of the suggested multilevel inverter, increasing the output voltage levels to 9 with only one DC sources is provided as demonstrated in Fig. 4. The introduced topology uses only one more capacitor, one more diode, and two additional switches compared to 7-Level topology, which increases the output voltage up to 4 times the input voltage. The switching modes for 9-Level topology are described in Table 2.

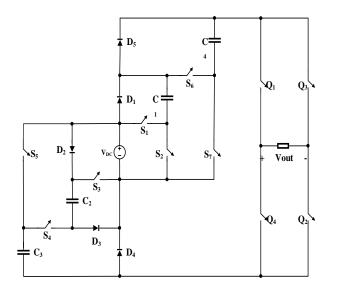

#### B. Extended 11-Level Topology

Fig. 5 illustrates 11-level topology of suggested multilevel inverter that is constructed by adding capacitor C<sub>4</sub>, diodes D<sub>4</sub> and D<sub>5</sub>, and switch S<sub>7</sub> compare to 9-level topology. This configuration increases the output voltage up to 5 times the input voltage with only one DC voltage

source. The 11-level topology switching algorithm is listed in Table 3.

Fig. 4: Extended 9-level topology.

Fig. 5: Extended 11-level topology.

#### **Capacitors Size Calculations**

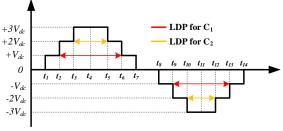

To determine the optimum value of capacitors, it is necessary to calculate the longest discharge period (LDP) for a given capacitor per switching cycle. During the LDP, the reserved energy within the capacitors is released and transferred to the load, resulting in generation of a specific voltage level. The LDP amounts for capacitors  $C_1$ and  $C_2$  are presented in Fig. 6, as indicated by the data given in Table 1.

Fig. 6: LDP of capacitors.

| $V_o$                  |       |       |       |       |       |       |                |       | С              | apaci          | tor st                | ate   |       |       |       |       |       |       |                |                       |

|------------------------|-------|-------|-------|-------|-------|-------|----------------|-------|----------------|----------------|-----------------------|-------|-------|-------|-------|-------|-------|-------|----------------|-----------------------|

| $rac{V_o}{V_{_{in}}}$ | $S_1$ | $S_2$ | $S_3$ | $S_4$ | $S_5$ | $S_6$ | S <sub>7</sub> | $Q_1$ | Q <sub>2</sub> | Q <sub>3</sub> | <b>Q</b> <sub>4</sub> | $D_1$ | $D_2$ | $D_3$ | $D_4$ | $D_5$ | $C_1$ | $C_2$ | C <sub>3</sub> | <b>C</b> <sub>4</sub> |

| +5                     | 1     | 0     | 1     | 1     | 0     | 1     | 0              | 1     | 1              | 0              | 0                     | R     | R     | R     | R     | R     | D     | D     | D              | D                     |

| +4                     | 1     | 0     | 0     | 0     | 1     | 1     | 0              | 1     | 1              | 0              | 0                     | R     | R     | R     | R     | F     | D     | D     | D              | С                     |

| +3                     | 1     | 0     | 0     | 1     | 0     | 1     | 0              | 1     | 1              | 0              | 0                     | R     | R     | R     | F     | F     | D     | D     | С              | С                     |

| +2                     | 0     | 1     | 0     | 1     | 0     | 1     | 0              | 1     | 1              | 0              | 0                     | R     | F     | F     | F     | F     | D     | С     | С              | С                     |

| +1                     | 0     | 1     | 0     | 1     | 0     | 0     | 1              | 1     | 1              | 0              | 0                     | F     | F     | F     | F     | F     | С     | С     | С              | С                     |

| +0                     | 0     | 1     | 0     | 1     | 0     | 0     | 1              | 1     | 0              | 1              | 0                     | F     | F     | F     | F     | F     | С     | С     | С              | С                     |

| -0                     | 0     | 1     | 0     | 1     | 0     | 0     | 1              | 0     | 1              | 0              | 1                     | F     | F     | F     | F     | F     | С     | С     | С              | С                     |

| -1                     | 0     | 1     | 0     | 1     | 0     | 0     | 1              | 0     | 0              | 1              | 1                     | F     | F     | F     | F     | F     | С     | С     | С              | С                     |

| -2                     | 0     | 1     | 0     | 1     | 0     | 1     | 0              | 0     | 0              | 1              | 1                     | R     | F     | F     | F     | F     | D     | С     | С              | С                     |

| -3                     | 1     | 0     | 0     | 1     | 0     | 1     | 0              | 0     | 0              | 1              | 1                     | R     | R     | R     | F     | F     | D     | D     | С              | С                     |

| -4                     | 1     | 0     | 0     | 0     | 1     | 1     | 0              | 0     | 0              | 1              | 1                     | R     | R     | R     | R     | F     | D     | D     | D              | С                     |

| -5                     | 1     | 0     | 1     | 1     | 0     | 1     | 0              | 0     | 0              | 1              | 1                     | R     | R     | R     | R     | R     | D     | D     | D              | D                     |

Time  $t_i$  is the transit time between two levels with different values.

According to Fig. 6, it can be concluded that LDP for capacitor  $C_1$  is equal to  $(t_2-t_6)$  or  $(t_9-t_{13})$ , and for capacitor  $C_2$  is equal to  $(t_3-t_5)$  or  $(t_{10}-t_{12})$ .

During LDP, the amount of charge transferred from capacitors  $C_1$  and  $C_2$  ( $Q_{C1}$ ,  $Q_{C2}$ ) is calculated as given in (2).

$$Q_{C_1} = 2 \times \int_{t_2}^{t_4} i_o(t) dt \quad ; \ Q_{C_2} = 2 \times \int_{t_3}^{t_4} i_o(t) dt \tag{2}$$

where  $i_0$  is the load current or the capacitor discharge current during the LDP. Considering the specific capacitor ripple voltage ( $\sigma$ ), the optimum capacitance for C<sub>1</sub> and C<sub>2</sub> is obtained from (3).

$$C_1 \ge \frac{Q_{C_1}}{\sigma \times V_{dc}} \quad ; \quad C_{12} \ge \frac{Q_{C_2}}{\sigma \times V_{dc}} \tag{3}$$

For resistive load,  $i_0$  in LDP is determined as given in the following:

$$i_{o}(t) = \begin{cases} 2\frac{V_{dc}}{R}; & for \ t_{2} \le t < t_{3} \\ 3\frac{V_{dc}}{R}; & for \ t_{3} \le t < t_{4} \end{cases}$$

(4)

Transit times  $t_2$ ,  $t_3$ , and  $t_4$  are obtained from (5) considering modulation with fundamental switching frequency and unit modulation index.

$$t_2 = \frac{\sin^{-1}(1/2)}{2 \times \pi \times f}; \ t_3 = \frac{\sin^{-1}(5/6)}{2 \times \pi \times f}; \ t_4 = T$$

(5)

where f is the switching frequency, and T represents the periodicity of the output voltage, by using (2)-(5). The optimum value of capacitance is calculated as determined in the following:

$$C_1 \ge \frac{2.67}{\pi \times f \times \sigma \times R}; \quad C_2 \ge \frac{1.76}{\pi \times f \times \sigma \times R}$$

(6)

#### **Power Loss Calculations**

The dominant power losses related to the introduced inverter are; a) conductive losses of switches, diodes, and capacitors; and b) voltage ripple losses of capacitors.

As mentioned before, the suggested inverter is modulated with a low switching frequency so, the switching loss is negligible. However, the conductive loss is calculated by considering on-state resistance of the switches,  $r_{on}$ , and diode,  $r_{d}$ , and the equivalent series resistance of capacitors,  $r_{c}$ . Conduction loss,  $P_{cond.i}$ , for the  $i^{th}$  voltage level is obtained as given in (7).

$$P_{cond.i} = r_{eq.i} \times i_{o.i}^2 \tag{7}$$

where  $r_{eq,i}$  is the equivalent series resistance in the charging path of the output current and  $i_{oi}$  is the load current for the *i*<sup>th</sup> voltage level. Because the *i*<sup>th</sup> voltage level is repeated 4 times in each switching cycle, the average of conduction loss per cycle is calculated as given in the following:

$$P_{cond.ave.i} = \frac{4(t_{i+1}-t_i)}{T} P_{cond.i}$$

(8)

where  $(t_i+1 - t_i)$  is the time interval of the *i*<sup>th</sup> voltage level. Similarly, for each voltage level, the average conduction loss of the inverter switches should be calculated.

The summation of conduction losses serves as an estimation for the overall power loss incurred by the inverter.

Ripple losses of capacitor manifest during the charge phase of the capacitor. The magnitude of the loss is contingent upon the variation between the input voltage and the instantaneous voltage across the capacitor during the charging process, as well as the capacitance value.

The equation representing the losses for the  $j^{th}$  capacitor is depicted in (9). The expression  $(t_j+1 - t_j)$  represents the duration of the charging time, while  $iC_j(t)$  denotes the charging current of the  $j^{th}$  capacitor. The total ripple losses of the inverter are determined by the summation of the ripple losses of all capacitors that are utilized.

$$P_{rip.j} = \frac{1}{2T} C_j \left[ \Delta V_{C_j} \right]^2 = \frac{1}{2T} C_j \left[ \int_{t_j}^{t_{j+1}} i_{C_j}(t) dt \right]^2$$

(9)

Therefore, total power loss of the inverter is obtained as given in the following:

$$P_{total} = P_{cond.ave} + P_{rip.j} \tag{10}$$

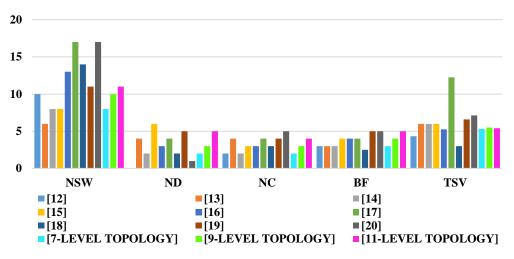

#### **Comparative Analysis**

This section presents a comprehensive comparative study among the proposed topologies and several recently discovered SC-based multilevel inverters. The study highlights the distinctive advantages and disadvantages of the proposed topologies, providing robust evidence to support the superiority of the suggested topologies over other competing alternatives. In Table 4, a comparison is performed by considering items such as number of voltage sources ( $N_{dc}$ ), diodes ( $N_D$ ), capacitors ( $N_C$ ), and switches ( $N_{SW}$ ), as well as the boost factor (BF) and TSV of all switches. In addition, a general comparison of the topologies introduced in [22]-[30] has been included in Fig. 7.

According to comparison results, proposed 7-level topology, despite having a boost factor equal to [22], requires fewer switches due to the reduced number of gate drivers. As a result, it costs less and is considered superior to other topologies.

In the configuration proposed in [23], there are more passive elements, and TSV on the switches is also high in compared with suggested 7-level topology. The values of  $N_D$ ,  $N_c$ , and BF are the same in both proposed 7-level and [24] configurations. Additionally, the voltage stress on the switches in [24] is higher than proposed 7-level topology.

Compared to the topologies introduced in [25]-[27], the suggested 9-level topology has less voltage stress and fewer passive elements than [25]-[27] topologies.

Table 4:

Comparative analysis of proposed topologies with similar SC-MLI

| Тор                    | NL | N <sub>dc</sub> | N <sub>SW</sub> | ND | Nc | BF  | TSV   |

|------------------------|----|-----------------|-----------------|----|----|-----|-------|

| [22]                   | 7  | 1               | 10              | -  | 2  | 3   | 4.33  |

| [23]                   | 7  | 1               | 6               | 4  | 4  | 3   | 6     |

| [24]                   | 7  | 1               | 8               | 2  | 2  | 3   | 6     |

| [25]                   | 9  | 1               | 8               | 6  | 3  | 4   | 6     |

| [26]                   | 9  | 1               | 13              | 3  | 3  | 4   | 5.25  |

| [27]                   | 9  | 1               | 17              | 4  | 4  | 4   | 12.25 |

| [28]                   | 11 | 1               | 14              | 2  | 3  | 2.5 | 3     |

| [29]                   | 11 | 1               | 11              | 5  | 4  | 5   | 6.6   |

| [30]                   | 11 | 1               | 17              | 1  | 5  | 5   | 7.14  |

| [7-Level<br>topology]  | 7  | 1               | 8               | 2  | 2  | 3   | 5.33  |

| [9-Level<br>topology]  | 9  | 1               | 10              | 3  | 3  | 4   | 5.5   |

| [11-Level<br>topology] | 11 | 1               | 11              | 5  | 4  | 5   | 5.4   |

|                        |    |                 |                 |    |    |     |       |

Fig. 7: Comparative analysis chart.

All these factors make proposed 9-level topology superior to the others. The topology given in [26] has lower voltage stress than proposed 9-level topology however, its demerit is applying more switches.

Although, the topology suggested in [28] has more switches than proposed 11-level topology, it has lower boost factor.

On the other hand, the topology introduced in [29] has same switches and diodes in compared to proposed 11level topology, but it has more TSV. Despite, the combination of lower  $N_{SW}$ ,  $N_{C}$  and TSV make the given 11level topology superior to the topology suggested in [30].

#### **Results and Discussion**

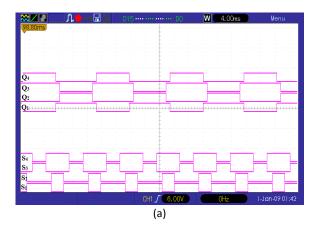

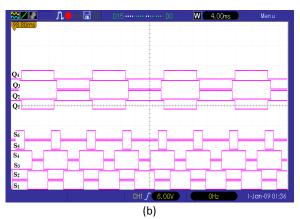

To verify practicability of the introduced topologies, a 7-level topology experimental prototype is implemented as depicted in Fig. 8. Table 5 lists the elements were employed in the laboratory prototype.

Fig. 8: Hardware setup

Table 5 Prototype circuit elements values

| Parameter        | value                           |

|------------------|---------------------------------|

| Input DC sources | <i>V</i> <sub>dc</sub> =30 V    |

| MOSFETs type     | IRFP260n                        |

| Output frequency | <i>f</i> <sub>o</sub> =50 Hz    |

| Opto-coupler     | TLP250                          |

| Capacitances     | 4700µf                          |

| Load             | <i>R</i> =100Ω <i>, L</i> =50mH |

| Microcontroller  | Atmega8a                        |

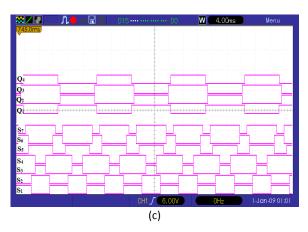

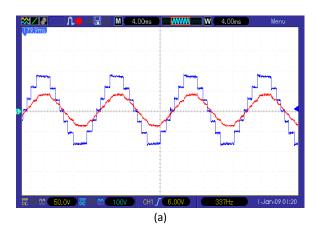

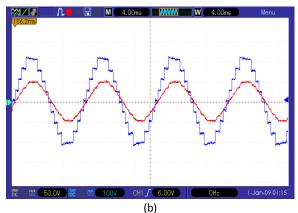

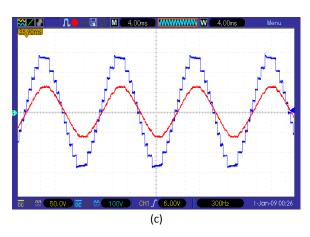

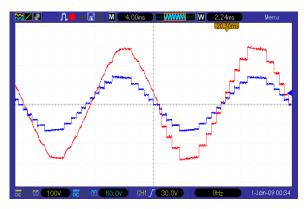

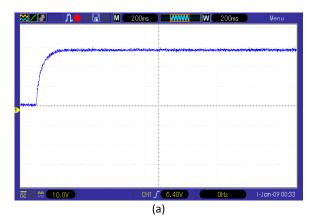

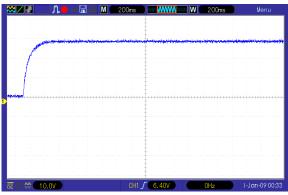

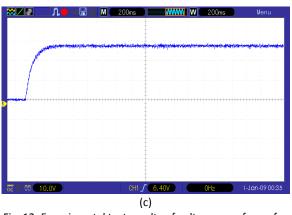

Atmega8a microcontroller is utilized to generate the gate signals of the implemented inverter switches that is shown in Fig. 9. Fig. 10(a)-(c) display the voltage and current waveforms of the resistive-inductive load (100 $\Omega$  -50 mH), respectively. The DC source has the value of 30 volts, consequently, the output voltage range is some lower than theoretical value due to losses incurred by the switches and diodes. The output current in Fig. 10 exhibits a sinusoidal waveform due to the presence of an inductive load within the circuit. Fig. 11 shows dynamic operation of the 11-level topology during load change from resistive-inductive to resistive. As shown in this figure, the suggested topology response to the load change is without performance failure. Among the proposed topologies, it is noteworthy that capacitor  $C_1$  in 7, 9, and 11-level configurations holds the highest level of significance due to its LDP. Therefore, it is crucial to consider this aspect while deciding on the final configuration. Fig. 12 depicts the maximum voltage of capacitors C<sub>1</sub> in the suggested 11-level topology. The output voltage of the capacitor has a self-balancing profile, which indicates that the capacitors experience minimal ripple.

Fig. 9: Gate signals of proposed (a) 7-level, (b) 9-level, and (c) 11-level topologies.

# Conclusions

This paper has presented modified switch-capacitor multilevel inverter topologies with 7, 9, and 11 levels in output voltage. All topologies have the potential to be used in renewable energy integration and electric vehicles.

Comprehensive examinations of circuit performance, voltage stress, capacitor sizing, and power loss were presented. The comparative assessments demonstrated that the suggested configurations achieve a greater voltage boost while utilizing fewer elements in comparison to the most advanced solutions available. The experimental test results confirmed the accuracy of the theoretical statements regarding the multilevel output voltage waveforms and the ability to balance capacitor voltages.

Therefore, the suggested SC multilevel inverters show great potential as solutions for applications such as solar photovoltaic systems and electric vehicle battery banks. Subsequent research will highlight the optimization of topologies for particular power ratings and the execution of efficiency tests.

Fig. 10: Experimental test results; voltage and current waveforms of resistive-inductive load for (a) 7-Level inverter (b) 9-level inverter and (c) 11-level inverter.

Fig. 11: Experimental test results of voltage and current waveforms for load change from resistive-inductive to resistive.

(b)

Fig. 12: Experimental test results of voltage waveforms for Capacitors C1 (a) 7-level topology, (b) 9-level topology, (c) 11level topology.

#### **Author Contributions**

F. Sedaghati chose the field of research. S. Ebrahimzadeh and H. Dolati collected information in this field. F. Sedaghati presented the proposed topology. S. Ebrahimzadeh and H. Dolati simulated and fabricated the proposed converter converter. The authors discussed the obtained results and drew conclusions. Under the supervision of F. Sadaghti, the text of the article was prepared by S. Ebrahimzadeh and H. Dolati. F. Sedaghati submitted the manuscript.

#### Acknowledgment

I appreciate the referees and their colleagues who helped the authors in publishing this article.

#### **Conflict of Interest**

The authors declare no potential conflict of interest regarding the publication of this work. In addition, the ethical issues including plagiarism, informed consent, misconduct, data fabrication and, or falsification, double publication and, or submission, and redundancy have been completely witnessed by the authors.

# Abbreviations

| PV  | Photovoltaic              |

|-----|---------------------------|

| EV  | Electric Vehicle          |

| PWM | Pulse Width Modulation    |

| SC  | Switched Capacitor        |

| MLI | Multilevel inverter       |

| THD | Total Harmonic Distortion |

| TSV | Total Standing Voltage    |

| LDP | Longest Discharge Period  |

| BF  | Boost Factor              |

#### References

- B. Saumya, Y. Zong, Sh You, L. Mihet-Popa, J. Xiao, "Technical and economic analysis of one-stop charging stations for battery and fuel cell EV with renewable energy sources," Energies, 13(11): 2855, 2020.

- [2] M. A. Velasquez, J. Barreiro-Gomez, N. Quijano, A. I. Cadena, M. Shahidehpour, "Distributed model predictive control for economic dispatch of power systems with high penetration of renewable energy resources," Int. J. Electr. Power Energy Syst., 113: 607-617, 2019.

- [3] L. He, J. Sun, Z. Lin, B. Cheng, "Capacitor-voltage self-balance seven-level inverter with unequal amplitude carrier-based APODPWM," IEEE Trans. Power Electron., 36(12): 14002-14013, 2021.

- [4] S. B. Kjaer, J. K. Pedersen, F. Blaabjerg, "A review of single-phase grid-connected inverters for photovoltaic modules," IEEE Trans. Ind. Appl., 41(5): 1292-1306, 2005.

- [5] T. Jin, X. Yan, H. Li, J. Lin, Y. Weng, Y. Zhang, "A new three-winding coupled inductor high step-up DC–DC converter integrating with switched-capacitor technique," IEEE Trans. Power Electron., 38(11): 14236-14248, 2023.

- [6] S. J. Salehi, M. A. Shmasi-Nejad, H. R. Najafi, "A new generalized step-up multilevel inverter topology based on combined t-type and cross capacitor modules," Int. J. Eng., 36(7): 1354-1368, 2023.

- [7] K. M. Nagabushanam, T. Mahto, S. V. Tewari, R. R. Udumula, M. A. Alotaibi, H. Malik, F. P. G. Márquez, "Development of high-gain switched-capacitor based bi-directional converter for electric vehicle applications," J. Energy Storage, 82: 110602, 2024.

- [8] S. Chen, Y. Ye, S. Chen, T. Hua, X. Wang, "Three-phase boost multilevel inverter based on coupled-structure switched-capacitor

and V2SVM," IEEE J. Emerg. Sel. Top. Power Electron., 11(1): 679-690, 2023.

- H. Dolati, E. Babaei, S. Ebrahimzade, "Reduced switch count single-[9] source seven-level switched-capacitor boost multilevel inverter with extendibility," Iran. J. Sci. Technol. Trans. Electr. Eng., 48: 1313-1321,2024.

- [10] S. K. Baksi, R. K. Behera, U. R. Muduli, "Optimized 9-level switchedcapacitor inverter for grid-connected photovoltaic systems," IEEE Trans. Ind. Appl., 60(2): 3284-3296, 2024.

- [11] K. Jena, D. Kumar, B. H. Kumar, K. Janardhan, A. R. Singh, R. Naidoo, R. C. Bansal, "A single DC source generalized switched capacitors multilevel inverter with minimal component count," Int. Trans. Electr. Energy Syst., 3945160, 7: 1-12, 2023.

- [12] R. Barzegarkhoo, M. Forouzesh, S. S. Lee, F. Blaabjerg, Y. P. Siwakoti. "Switched-capacitor multilevel inverters: comprehensive review," IEEE Trans. Power Electron., 37(9): 11209-11243.2022.

- [13] M. V. Patel, M. L. Patel, N. D. Shah, "A review of Switched Capacitor (SC) circuits," Int. J. Sci. Res., 2(1): 81-83, 2012.

- [14] B. M. Varghese, B. M. Jos, "Switched capacitor multilevel inverter with different modulation techniques," in Proc. International Conference on Innovations in Information, Embedded and Communication Systems (ICIIECS): 1-6, 2017.

- [15] D. Singh, N. Sandeep, "Switched-capacitor-based multi-source multilevel inverter with reduced part count," IEEE J. Emerg. Sel. Top. Ind. Electron., 4(3): 718-724, 2023.

- [16] M. Ali, M. Tayyab, A. Sarwar, M. Khalid, "A low switch count 13level switched-capacitor inverter with hexad voltage-boosting for renewable energy integration," IEEE Access, 11: 36300-36308, 2023.

- [17] K. Jena, D. Kumar, K. Janardhan, B. H. Kumar, A. R. Singh, S. Nikolovski, M.Bajaj, "A novel three-phase switched-capacitor fivelevel multilevel inverter with reduced components and selfbalancing ability," Appl. Sci., 13(3): 1713, 2022.

- [18] P. Kumari et al, "Self-balanced high gain switched-capacitor boosting inverter with lower cost function," Int. J. Electron., 111(8): 1301-1318, 2023.

- [19] Y. Wang, J. Ye, R. Ku et al., "A modular switched-capacitor multilevel inverter featuring voltage gain ability," J. Power Electron. 23: 11-22, 2023.

- [20] M. N. H. Khan, R. Barzegarkhoo, Y. P. Siwakoti, S. A. Khan, L. Li, F. Blaabjerg, "A new switched-capacitor multilevel inverter with soft start and quasi resonant charging capabilities," Int. J. Electr. Power Energy Syst., 135: 107412, 2022.

- [21] M. A. Hosseinzadeh, M. Sarebanzadeh, C. Garcia, E. Babaei, J. Rodriguez, "Efficient switched-capacitor multilevel inverters for high-power solar photovoltaic systems," IET Renewable Power Gener., 16(11): 2248-2266, 2022.

- [22] F. Sedaghati, S. Ebrahimzadeh, H. Dolati, H. Shayeghi, "A modified switched capacitor multilevel inverter with symmetric and asymmetric extendable configurations," J. Oper. Autom. Power Eng., 13(1): 20-27, 2025.

- [23] M. Chen, P. C. Loh, Y. Yang, F. Blaabjerg, "A six-switch seven-level triple-boost inverter," IEEE Trans. Power Electron., 36(2): 1225 -1230. 2020.

- [24] Y. P. Siwakoti, A. Mahajan, D. J. Rogers, F. Blaabjerg, "A novel seven-level active neutral-point-clamped converter with reduced active switching devices and DC-link voltage," IEEE Trans. Power Electron., 34(11): 10492-10508, 2019.

- [25] Y. Wang, K. Wang, G. Li, F. Wu, K. Wang, J. Liang, "Generalized switched-capacitor step-up multilevel inverter employing single DC Source," CSEE J. Power Energy Syst., 8(2): 439-451, 2022.

- [26] S. Islam, M. D. Siddique, A. Iqbal, S. Mekhilef, "A 9- and 13-level

How to cite this paper:

F. Sedaghati, S. Ebrahimzadeh, H. Dolati, "Modified topologies for single source switchedcapacitor multilevel inverters," J. Electr. Comput. Eng. Innovations, 13(1): 257-266, 2025. DOI: 10.22061/jecei.2024.11234.780

URL: https://jecei.sru.ac.ir/article 2231.html

switched-capacitor-based multilevel inverter with enhanced selfbalanced capacitor voltage capability," IEEE J. Emerg. Sel. Top. Power Electron., 10(6): 7225-7237,2022.

- [27] H. Khoun Jahan, M. Abapour, K. Zare, "Switched-capacitor-based single-source cascaded h-bridge multilevel inverter featuring boosting ability," IEEE Trans. Power Electron., 34(2): 1113-1124, 2019.

- [28] M. R. Hussan, A. Sarwar, I. Khan, M. Tariq, M. Tayyab, W. Alhosaini, "An eleven-level switched-capacitor inverter with boosting capability," Electronics, 10(18): 2262, 2021.

- [29] S. Deliri, K. Varesi, S. Padmanaban, "An extendable single-input reduced-switch 11-level switched-capacitor inverter with quintuple boosting factor," IET Gener. Transm. Distrib., 17(3): 621-631, 2023

- [30] M. N. H. Khan, M. Forouzesh, Y. P. Siwakoti, L. Li, F. Blaabjerg, 'Switched capacitor integrated (2n + 1)-level step-up single-phase inverter," IEEE Trans. Power Electron., 35(8): 8248-8260, 2020.

#### **Biographies**

Farzad Sedaghati was born in Ardabil, Iran, in 1984. He received the M.S. and Ph.D. degrees both in Electrical Engineering in 2010 and 2014 from the University of Tabriz, Tabriz, Iran. In 2014, he joined the Faculty of Engineering, University of Mohaghegh Ardabili, where he has been an Assistant Professor, since 2014. Also, he is Associate Professor since 2019. His current

research interests include power electronic converters design and applications and renewable energies.

- Email: farzad.sedaghati@uma.ac.ir

- ORCID: 0000-0001-6974-4719

- Web of Science Researcher ID: NA

- Scopus Author ID: 35410298600

- Homepage: https://academics.uma.ac.ir/profiles?Id=617

Soghra Ebrahimzadeh was born in Ardabil, Iran in 1994. She obtained her B.Sc. and M.Sc. degrees in Power Electrical Engineering University of Mohaghegh Ardabili in 2016 and 2019, respectively. Currently, she is pursuing a Ph.D. degree in Electrical Engineering at the University of Mohaghegh Ardabili, Ardabil, Iran. Her current research interests include switched-capacitor multilevel inverters and grid-tied multilevel

- Email: soghraebrahimzade2@gmail.com • ORCID: 0009-0008-6726-1519

- Web of Science Researcher ID: NA

- Scopus Author ID: NA

- Homepage: N/A

Hadi Dolati was born in Ardabil, Iran, in 1997. He received his B.Sc. degree in Electronic Engineering from the University of Mohaghegh Ardabili, Ardabil, Iran, and the M.Sc. degree in electrical engineering from the University of Tabriz, Tabriz, Iran, in 2019, and 2024, respectively. His current research interest include design, control, and applications of power electronics converters.

- Email: hadidolati1997@gmail.com

- ORCID: 0009-0001-4245-7311

- Web of Science Researcher ID: NA Scopus Author ID: N/A

- Homepage: N/A